Cache一致性协议与MESI(2)

作者 muxiqingyang009 | 2011-07-11 16:58 | 类型 科技普及, 芯片技术 | 11条用户评论 »

|

Write invalidate提供了实现Cache一致性的简单思想,处理器上会有一套完整的协议,来保证Cache一致性。比较经典的Cache一致性协议当属MESI协议,奔腾处理器有使用它,很多其他的处理器都是使用它的变种。 单核处理器Cache中每个Cache line有2个标志:dirty和valid标志,它们很好的描述了Cache和Memory(内存)之间的数据关系(数据是否有效,数据是否被修改),而在多核处理器中,多个核会共享一些数据,MESI协议就包含了描述共享的状态。 在MESI协议中,每个Cache line有4个状态,可用2个bit表示,它们分别是:

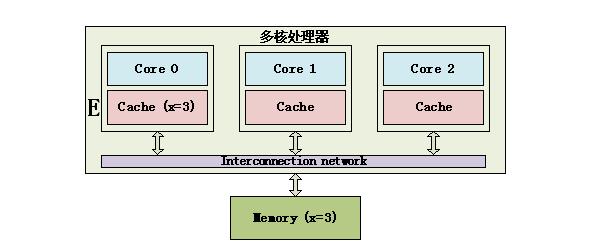

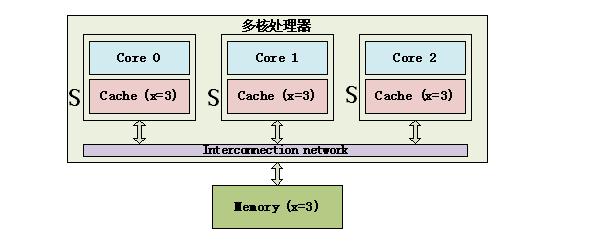

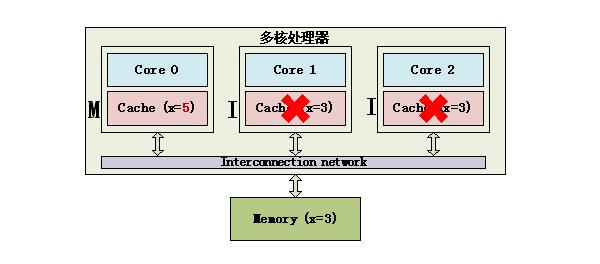

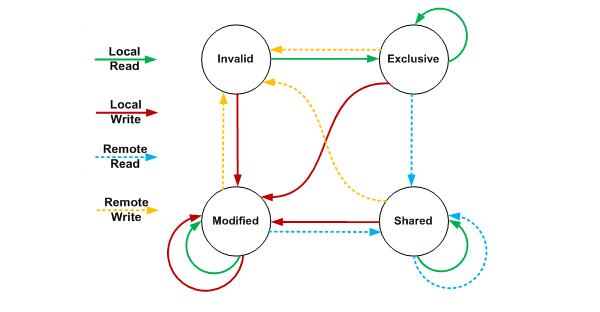

MESI状态 M(Modified)和E(Exclusive)状态的Cache line,数据是独有的,不同点在于M状态的数据是dirty的(和内存的不一致),E状态的数据是clean的(和内存的一致)。 S(Shared)状态的Cache line,数据和其他的Cache共享。只有clean的数据才能被多个Cache共享。 I(Invalid)表示这个Cache line无效。 E状态示例如下: E状态 只有Core 0访问变量x,它的Cache line状态为E(Exclusive)。 S状态示例如下: S状态 3个Core都访问变量x,它们对应的Cache line为S(Shared)状态。 M状态和I状态示例如下: M状态和I状态 Core 0修改了x的值之后,这个Cache line变成了M(Modified)状态,其他Core对应的Cache line变成了I(Invalid)状态。 MESI协议状态迁移图如下: MESI协议状态迁移图 在上图中,Local Read表示本内核读本Cache中的值,Local Write表示本内核写本Cache中的值,Remote Read表示其它内核读其它Cache中的值,Remote Write表示其它内核写其它Cache中的值,箭头表示本Cache line状态的迁移,环形箭头表示状态不变。 MESI状态之间的迁移过程如下:

MESI状态迁移 AMD的Opteron处理器使用从MESI中演化出的MOSEI协议,O(Owned)是MESI中S和M的一个合体,表示本Cache line被修改,和内存中的数据不一致,不过其它的核可以有这份数据的拷贝,状态为S。 Intel的core i7处理器使用从MESI中演化出的MSEIF协议,F(Forward)从Share中演化而来,一个Cache line如果是Forward状态,它可以把数据直接传给其它内核的Cache,而Share则不能。 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

雁过留声

“Cache一致性协议与MESI(2)”有11个回复

这篇好一点。但如果能用大白话把MESI和其各种变种阐述一下就会更好。

不错,已经通俗易懂啦

http://upload.wikimedia.org/wikipedia/commons/9/99/MESI_protocol_activity_diagram.png

好很多了, 赞. 但是少了 I->S的状态转换

I 在本地读时 ->

-> (其他cpu没有副本)本cache: I->E

-> (其他cpu, S->S, E->S, M->写内存->S), 本cache: I->S

多谢lai jiangshan 指正,果然是少了 I->S的状态转换。

记住首席的爱好是现代通俗版古代白话文:)

I 在本地读时 ->

-> (其他cpu没有副本)本cache: I->E

-> (其他cpu, S->S, E->S, M->写内存->S), 本cache: I->S

//如果其他CPU的状态是M,一定会写内存么?

还是直接M->S

把缓存一致性协议和barrier结合起来介绍就更棒了。

to 6L(powerpc)

不一定写内存, 不同的体系,有写的有不写的, lz文中说是写的哪种.

见lz文的M->S:

这行数据被写到内存中,使其它核能使用到最新的数据,

状态变成S

—–

我的理解, 如果M->S总是写内存的话, latency高点, 因为读写内存次数变多.

如果M->S不写内存的话, 总线繁忙一些, 因为每次读都会导致/收到*多个*其他的S的CPU的回应.

MOESI MESIF 都能减缓这些问题

amd use moesi

intel use mesif

谢谢Ma Ling ,笔误

由于这里的文章不能修改,修改后的文章发表在我的博客上。

http://blog.csdn.net/muxiqingyang/article/details/6615199