Intel 。8个Core的Nehalem-EX

作者 陈怀临 | 2010-01-31 17:42 | 类型 行业动感 | 17条用户评论 »

|

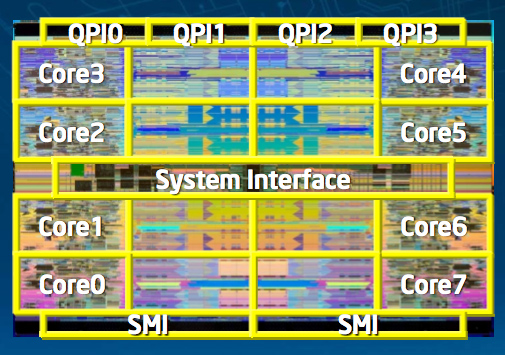

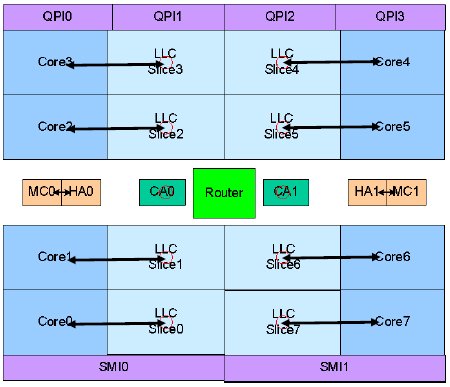

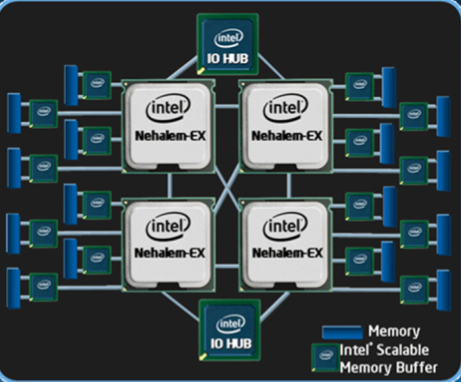

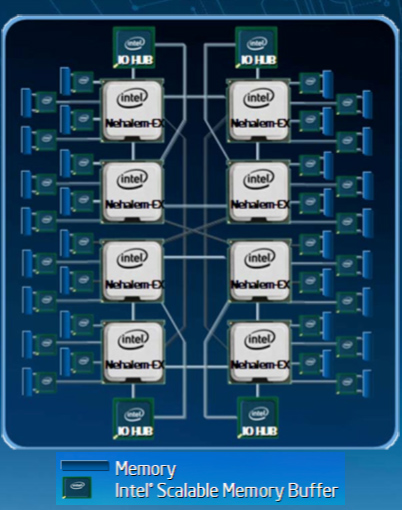

2010年的Q1,如果不出意外,Intel将发布其最高端的服务器XEON芯片,8个Core的Nehalem-EX。这将是CPU技术的一个突破。笔者对此是充满了期待,弯曲评论上也曾经有过相关报道【作者为硅谷老人】。如果能主持,sorry,如果能够参与,这样一个项目,应该说是金钱与美女,我都不换。至少金钱的魅力比不上Nehalem-EX的光芒。美女的问题可以戒急用忍。。。 下面来看看这款芯片的一些情况,以飨弯曲评论发烧友天天浪费带宽的不容易。 如果阅读Nehalom在Wiki的页面,细心的读者也不会太注意一个Intel的design项目叫做”Beckton“。这就是Intel的Nehalem微机构的Tip of the Sword!精英中的精英;皇冠上的珍珠。一个拥有8个Core;支持超线程的,可以4个CPU互联,8个CPU互联的,世界上将最牛叉的CPU。 下图所示为Nehalem-EX的Die的组成部分。非常的优美。。。 上图所示,可以看见4个QPI Interface,或者我们说CSI Interface。SMI是Nehalem-EX的Memory Interface。4个QPI接口可以被用来与其他的3个CPU互联,剩下的一个QPI要被用来连接IOH。 Die中间的部分是24M的Layer-3的Cache缓存。从图中可以看出,在实现上,是把24Mcache 拆成8份。每个3M与一个core(1/8) tightly coupled。8个3M cache通过一个ring bus连接起来,形成一个一致性的24M的cache。下图所示是Nehalem-EX关于Cache的实现逻辑图: 下面来看看基于Nehalem-EX的4 和8 socket(CPU)系统互联: | |

雁过留声

“Intel 。8个Core的Nehalem-EX”有17个回复

首席,24MB shared last level cache,是不是真的啊?

首席比较一下intel的8 core和freescale不久前发布的P4080处理器(8核)在设计上的差异和各自的有缺点,结果应该比较有意思

http://www.freescale.com/webapp/sps/site/prod_summary.jsp?code=P4080&fsrch=1

首席有空聊聊,IBM的Power7与Intel的Nehalem-EX的各自的优缺点。来个比较吧。应该很有意思的。

是,是24M的L3 Cache。但是,在实现上,是把24Mcache 拆成8份。每个4M与一个core(1/8) tightly coupled。8个4M cache通过一个ring bus连接起来,形成一个一致性的32M的cache。

没什么新概念,只是编程越来越费事了。

24M的Cache,Intel之前貌似只在Itanium里面干这种事,功耗恐怕不会小。

中间那一大陀是LLC。莫非Core内部还有私有L2?

弯曲评论出新文章速度太快,这篇文章沉得太快了。

真是24MB,那很吓人了。

P4080去年freescale的人来给我们讲了一次,精力原因没有过多观注。只记得两点:1.L2 cache是backside的,鄙人愚钝一时没有弄明白为什么要搞成backside。2.DPAA中有一个类似于“报文排序引擎”的东西,当时讲的人讲得很含糊。

麻烦楼上的各位大佬给我讲讲。。。

24M CACHE,那我的所有代码和核心数据(特别是特征库)都可以放进去了,真好,性能直接提升了!

是。在利用x86做平台的观点上,我是投你的票的。从长远来说,Cavium等都活不下去。EZChip再过N年也没有活路。我成天惦着short他的股票。目前还么有机会。其流通量太小,整的股价太高。

8个4M,应是32M,请原谅我的浅,怎么是24M呢?

首席,你是在投Panabit吗?

每Core独享的L3 cache,假设有一半的cache空间用来装数据,那么意味着有4个Core的计算资源可能是浪费的哦。我个人认为Multicore编程还是要充分考虑资源平衡的。还有一个,就是Nehalem-EX的IO怎么样我不知道,不知道它是否很适合做报文转发,BCM1480 I/O就不错,我估计后来的P4080和Cavium都参考了一下BCM1480的IO设计。

对于可编程报文处理芯片的发展,我同意哈!

Panabit在系统设计方面我还是很赞的。是一期学生中最好的:)

首席太过奖了,同您比,差距好大!还有很长的路要走!

首席,我也想跟你学。 通过什么途径?

你先多看panabit.我现在不直接招(男)学生了

首席不招收男学生,你让我怎么分析华赛的盒子啊?

又是multicore,又是multi cpu,intra cpu和inter cpu的编程模型是一致的吗,比如都是SMP? 8*8 core,再加上hyper threading,现有的操作系统能撑得住吗?