ARM的薄积与薄发–浅谈ARM的Interconnect的战略

作者 陈怀临 | 2010-11-28 19:07 | 类型 芯片技术, 行业动感 | 22条用户评论 »

|

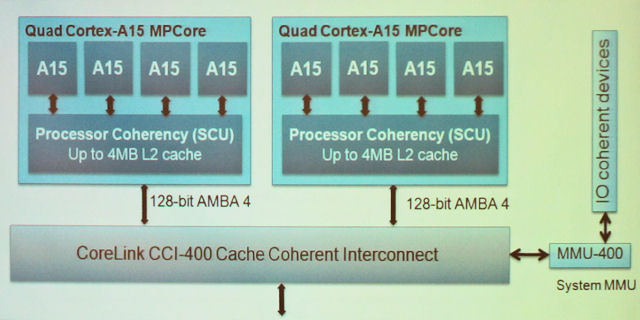

因为Blah blah的原因,笔者最近捡起了ARM。。。对ARM的ARMV5的Core,例如IXP 425,465和IXP23XX,笔者可以说是非常的熟悉。写过许多产品级别的汇编。。。但对基于ARMV7的Cortex-A|M|R没有接触过。但相信这对笔者应该不是个大问题。。。 这个Holiday假期,读了一些Intel的一个大拿王Sir的关于ARM的文章。第一是很钦佩;第二是很confusing。。。他在Intel拿着俸禄,为何对ARM的来龙去脉这么熟悉。。。?唯一的解释就是喜欢。。。 在谈到ARM的Cortex-A15的时候,他的文章中唯一欠缺的就是没有谈到在高端系统中最不可缺少的一个方面–Interconnect。这是个美中不足的地方。。。 这个的意思类似于:当谈AMD的Magny-Cores的时候,不谈HT;当谈INTC的Nehalem的时候,不谈QPI。龙门阵就失去了一半的精彩。。。 大家知道,ARM的市场基本上是SoC这块小天地。。。在SoC这个沃土上,大家更集中考虑的是On-Chip的通信。。。换言之,是Intra-Chip的通信。很难相信你整几个SoC芯片在板子上,然后大家一起互通。这不是以前SoC的做法。SoC+DSP的年代更是一个:SoC的CPU做控制。其他逻辑做协处理器。。。 在Cortex-A9的年代。一个Cortex-A9 MP是能而且只能支持(Up to)4个Cortex-A9的CPU Core的。Cache的一致性也只能通过其SCU(Snoop Control Unit)在这4个Core之间实现。如果你想做一个SoC里面放6,8,12个Core,这个Cache的事情基本上就要把人折腾疯了。。。很难相信一个系统软件工程师会喜欢这样的一个Explicit Clustering Partition的编程模型。。。 这一切都在悄悄的改变。。。 11月,Cortex-A15发布了。。。许多读者更多的注意到了A15各方面性能的提升,as opposed to A8 and A9。其实,伴随着Cortex-A15的发布,还有一个很重要的部分–高端互联逻辑。 这就是 CoreLink 400的CoreLink CCI-400 Cache Coherent Interconnect !!! “The CoreLink CCI-400 provides full coherency between the L2 caches of two multicore Cortex-A15 processors and I/O coherency with up to three other master, such as the Mali GPU, sharing data in either of the L2 caches of the Cortex-A15 processors. The CCI-400 routes traffic to up to three slaves (e.g. two high performance channels to the memory controler and one to the rest of the system) using virtual channels to prevent blocking and barriers to preserve ordering.” 拥有了CoreLink的互联,在一个SoC里面,多个Cortex-A15 Cluster(4个为一个Cluster)之间就可以达到一个完整的SMP的模型。 拥有了CoreLink的互联,可以把一个Cortex-A系列芯片,与ARM的GPU芯片ARM Mali-T604互联,并形成一个Cache Coherence的模型。。。 这是ARM能通向高端系统的重要基础。。。 下图所示为一个高端SoC的结构图。这个SoC,拥有8个核(Cortex-A15)。每4个为一个Cluster,通过ARM的SCU互联。另外,拥有一个GPU的Core。所以的逻辑,都通过CoreLink的CCI-400互联,形成一个共享内存的系统: | |

雁过留声

“ARM的薄积与薄发–浅谈ARM的Interconnect的战略”有22个回复

(8个打分, 平均:4.75 / 5)

(8个打分, 平均:4.75 / 5)

头牌看到很牛的王Sir又按耐不住比试武功了。

王的Arm系列内容充实,文笔流畅,确实出色。

我请教(考)弟兄们一个问题:通常是SoC领域,例如以前的ARM芯片,CPU与DSP或者其他逻辑基本上是通过一个Local Bus来拉通。。。

现在Cortex-A15为啥要通过Cache Coherence的方式来与GPU互联。想主攻啥市场?

另外,会出现多个基于Cortex-A15 MP的Processor互联的情况嘛?例如明年。。。谁突然推出一个芯片:每个是8个Cortex-A15的Core;然后外面出3个CoreLink CCI Interface。。。

很可怕。。。

王好像去intel不久吧,他是freescale的,估计对ppc更熟。

王齐的两本书也不错,一本powerpc的,一本PCIE体系结构导读。后者是PCIE快速入门的首选,当然弯曲的大牛是不用看这种书的,呵呵。

首席啥时候也整一本体系结构或微处理架构方面的书,造福下我们这些啃不动E文的IT民工?

首席,能谈谈MIPS架构和ARM的优缺点吗?

现在MIPS的股票和08年比,都涨十倍左右了,为什么龙芯选MIPS,而不是speac,alpha等后裔?

楼上这个问题得请教胡老师,或者去弄一本《龙芯的足迹》。我记得胡老师在里面写过,他以前青睐的是SPARC。

MIPS还是算了,在ARM的强攻下,MIPS会成为历史的

离用ARM服务器不远了。当初搞嵌入式时那个对ARM赞啊,难道现在搞服务器也可以对ARM赞一把,

(¯﹃¯)口水。。。

感觉特别怪。。。Imagine一下一台几十个ARM Processor,然后每个是8个Cortex-A 64bit的Core。。。感觉很怪异。。。

to 五楼:

关于选择MIPS,我记得当初龙芯1刚出来的时候,听过胡的一次演讲。胡当时说他们选方向的时候,参考了那个性能前1000名的排行榜,当时有60%的机器都是MIPS的,高性能运算的应用软件也多,于是就…。我推断当时他们对产品定位的经验不足,想走高端进入高性能计算的领域。后来形势不对,又迅速掉头扎入NC领域。因此这个系列就显得向上性能不足,向下功耗太大。有些两头不讨好。现在从偶尔发出的新闻稿看,龙芯还是想回到高性能计算的领域的。也许这就是当初他们担负的任务,他们设计的初衷。

记得当时关于MIPS指令的license,还有过一番争论。姚飞同学曾经指出MIPS指令是需要license的,而且很贵,不如选择SPARC。另一方则避而不谈这个问题。估计当初没有想到。后来MIPS公司果然发来律师函。再后来就是和STE合作,好像解决了这个问题。具体内幕不得而知。大宋朝千年传承的合纵连横之策,也许没吃什么亏。

核多点yy倒是可以, 但是imagine, 还有一些路要走的, 设计一个板子容易, code高质量的跑出来就有麻烦了。

这个Holiday假期,读了一些Intel的一个大拿王Sir的关于ARM的文章。第一是很钦佩;第二是很confusing。。。他在Intel拿着俸禄,为何对ARM的来龙去脉这么熟悉。。。?—-他以前在FREESCALE,当然熟悉ARM了,FREESCALE的PPC都停滞不前了

To shuyong & all,

但MIPS在wireless/wifi/digital TV/setbox等领域的市场目前还是很大的。

另一个,4G/LTE等,MIPS是否有优势?MIPS在智能手机/终端上,随着4G/LTE的发展,是否有机会?有熟悉4G/LTE的同学帮忙分析分析吗?

MIPS在wifi没前途,最多在AP端,量不大。

才发现ARM都已经能这么牛啦,我还停留在ARM11阶段…

同为RISC架构,MIPS还是偏向高性能方向的,ARM则是偏向低功耗,不过,最近的文章说的都很清楚,处理器的发展都很成熟了,你可以用的架构我也一样可以加上,归根到底就是要不要这样子做?做了需要花多少代价?基本上和用的ISA没有太大关系……

核多点yy倒是可以, 但是imagine, 还有一些路要走的, 设计一个板子容易, code高质量的跑出来就有麻烦了。

———>

靠GO/erlang之流了.

to 4楼&老韩

谢谢对初入门的指点

nic-401 (CCI) 还没release.

orwell dmc-400 今天才alpha.

而且说实话,intel在CCI方面还是领先的.

首席,能否描述一下CCI-400的互连和Cache一致性如何解决的?谢谢!

CCI release了。

ARM赖以成功的是Ecosystem,CCI400系统中,支持Cache Coherency是一套新的总线协议,目前来看只有ARM的一些IP支持此功能。别家的GPU,目前没有支持这个Cache Coherency的功能。Cortex-A15 的Cluster或许可以用起来此功能,这种产品针对服务器市场,但是ARM对于服务器市场的战略以及软件支持,目前还不够清晰。

总之CCI目前还是看起来很美。

可否提供一下Intel wang写得关于ARM文章的链接,谢谢。