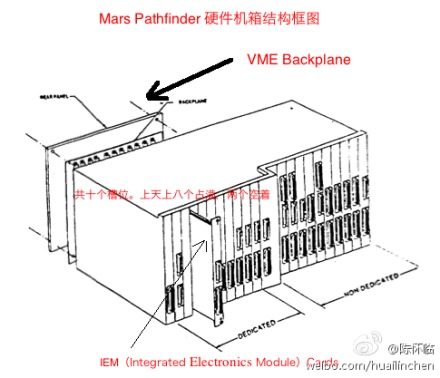

Pathfinder系统是一个国家机械,电子,材料,通讯整体最高实力的结晶。非常复杂。我们从现在开始专注于其的数控系统。Pthfinder是一个典型Backplane的Chasis结构。Backplane是采用的VME互联。上天的时候,八个槽位占满,两个是空着的。Of the 8,其中一个是CPU主控板。

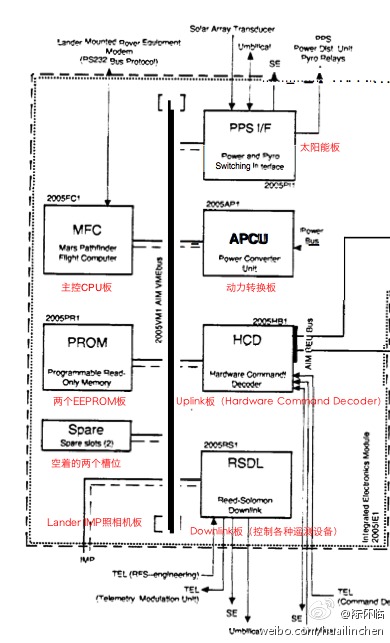

下图是VME互连细节图. (1)MFC CPU card(2)两个EEPROM card[所有的软件,双备和来自地球的动态升级] (3)太阳能card (4)能源转换card(从3接能源,给VME设备提高Power)(5)Uplink card(1553B interface在这个card上)(6)Downlink card(连遥测)(7)IMP照相机

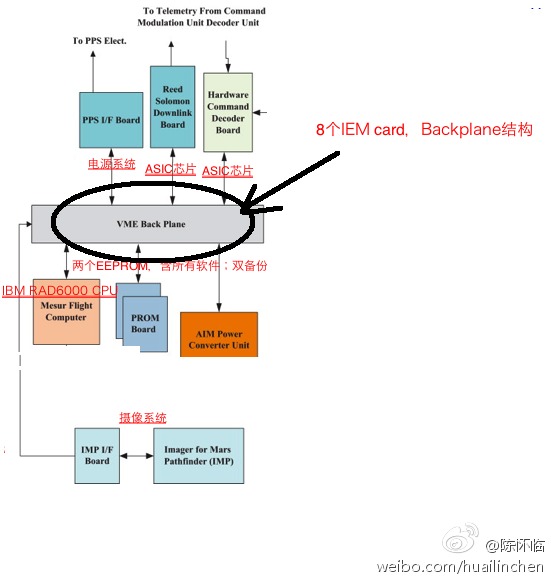

下图所示是另外一个角度描述的VME背板上的各个IEM(Integrated Electrics Module)卡。要注意的是两个电源系统。太阳能PPS卡是产生Power,但通过另外的接口给APCU。APCU是真正的给VME和其上的IEM提高Power Distribution的。APCU是自己带了rechargeable电池的。

双EEPROM软件系统和控制序列命令的Active/Passive备份是一个非常好的设计。在Pathfinder快要进入Mars大气层的时候,JPL的控制中心其实还迅速的给过一个patch,做软件的update。

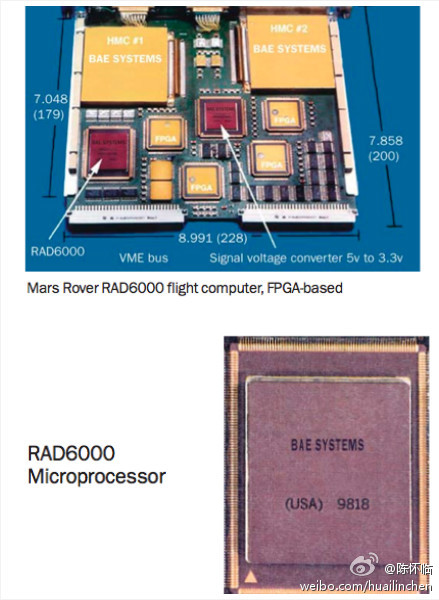

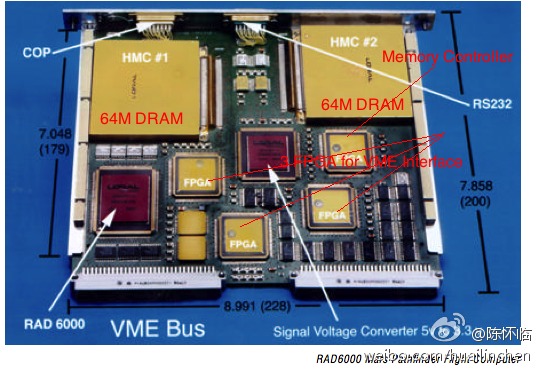

从现在开始,逐步围绕这VME interconnect下的IEM card开始阐述。首先是最重要的CPU卡。在Pathfinder系统里,CPU卡来自Lockheed Martin的基于IBM/BAE的RAD6000 CPU的Single Board Computer。什么意思,你就理解这个板子上啥都集成了。例如,chipset,rs232,vme等。

上图一是CPU卡的top view。图二是RAD6000 CPU。 RAD:Radiation Hardened,防辐射。在2008年之前,美国航天系统基本上都是用RAD6000.其中包括2003年发射的Mars Opportunity和Spirit号。Opportunity目前正在Mars上等待Curiosity的到来。。。

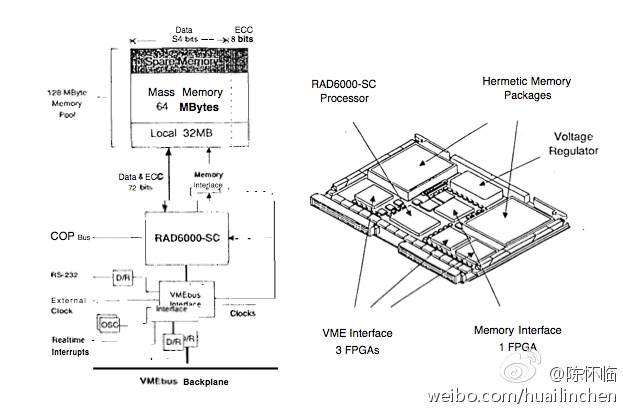

在CPU板子上,除了RAD6000 CPU之外,主要是VME Interface, Memory Interface和RS232 Interface。VME Interface是3个FPGA分别实现;Memory Controller一个。128M DRAM是两个HMC(Hermetic Memory Packages ) Packages。请参阅图解。

Hermetic Package其实就是密封封装(不知如何翻译了),例如通过陶瓷和金属。RAD6000上黄灿灿的都应该是金属封装。亲,Mars的晚上是零下120度。DRAM要歇了,大家都歇了。3个VME interface的FPGA和Memory Controller也都是金属封装的。

下图所示是平面图。和后来的基于RAD6000的CPU板子相比,要记住的是:1997年的Pathfinder是绝对没有PCI Interface的。3个VME FPGA基本搞定Interconnect,和遥测和1553B的各种设备互联。RS232和Rover(小跑车)互联。图中各FPGA的标注和实际单板的位置有出入。

图中的COP Interface是调试接口。要注意Clock。RAD6000 CPU工作在:2.5, 5, 10, and 20M赫兹下。为什么?省功耗。 Pathfinder 9月27日出事后JPL的人也是一通瞎猜,例如clock分频乱了套了,Clock出了问题,是,全完了。类似与:本来是9浅1深,现在是全浅了。玩个鸟呀。

RAD6000-SC被NASA广泛的应用在各种航天器系统上,包括Mars Spirit和Opportunity。但单板结构interface有所变化例如PCI等。RAD6000-SC单板的价格多少?大概是20到30万美金左右。不服的可以自己山寨一个到火星上玩玩。下图所示是采用了RAD6000-SC的航天系统的列表。

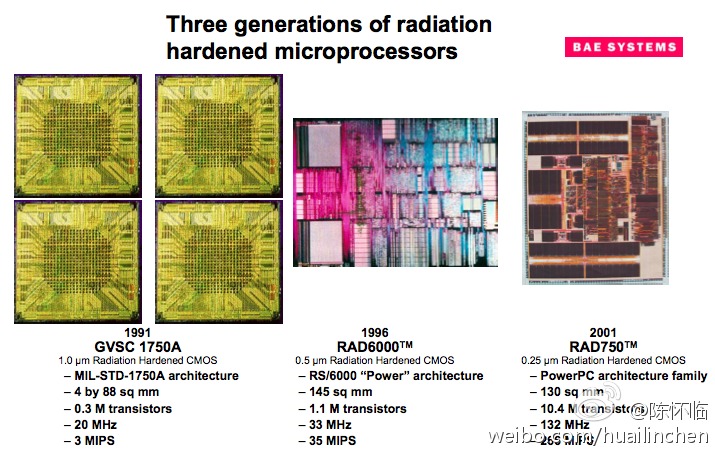

RAD6000起源于IBM后来被卖给了Lockheed Martin然后再落入BAE System的手里。在军控CPU方面目前认为是3代。8月6日要降落在Mars上的Curiosity(好奇者)是RAD750,CPU Core是PowerPC 603 结构IBM PPC750. Pathfinder的RAD6000的CPU core来自Power结构的Power1微结构。750等都是603演化而来的。这也是为什么603 Bus,到了7447或者G4芯片,MPX bus才上来。

如图所示是目前3代军控防辐射CPU的roadmap和相应的die图。750还不能支持多核系统。目前有不少研发讨论关于多核系统在AeroSpace系统的应用,但还没有得到真正的落地。

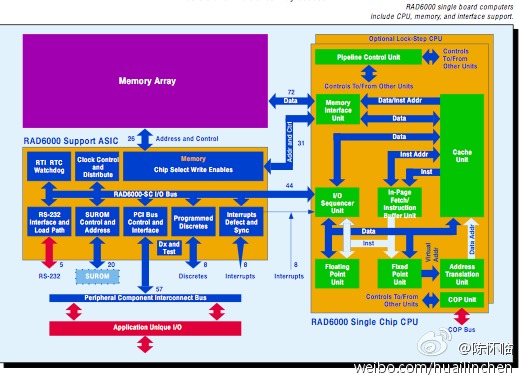

图示是RAD6000-SC的逻辑图。这张图是一个General的结构图,那些蓝色的模块就是相应的Interface(可以是各种实现,例如,FPGA or/and ASIC)。右边的CPU Core芯片微结构图。

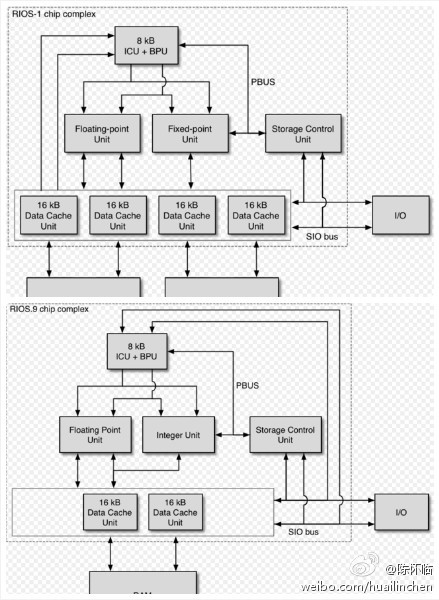

1997年的Pathfinder的RAD6000-SC单板CPU Core来自IBM Power1的微结构。Power1或者叫做RS6000 CPU,有两个配置RIOS1,针对RS/6000 服务器:10个芯片互连。RS.9,针对RS/6000工作站,:8个芯片互连。如图所示分别为RIOS1和RS.9的微结构。请记住:是多芯片解决方案。

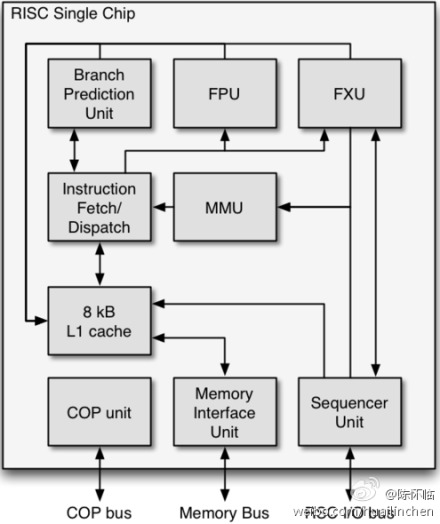

RS/6000为了覆盖低端市场和无盘工作站市场,1992年,在Power1多芯片solution的基础上推出了一个单芯片方案,这就是所谓的RSC(RISC Single Chip)。1997年的Mars Pathfinder的RAD6000就是基于这个RS/6000 RSC,然后加上航天所需要的防辐射和其他封装技术的产物。

|

宇航级的CPU为什么不用砷化镓工艺制造呢?宇宙的高能粒子直接就把CMOS搞定了。

深入浅出,好文。

估计是材料一变,光刻工艺要跟着变,没有商业化生产实践的验证,反而不如硅的变数小.

不服不行