作者 hid | 2012-05-03 18:43 | 类型 行业动感 | 4条用户评论 »

|

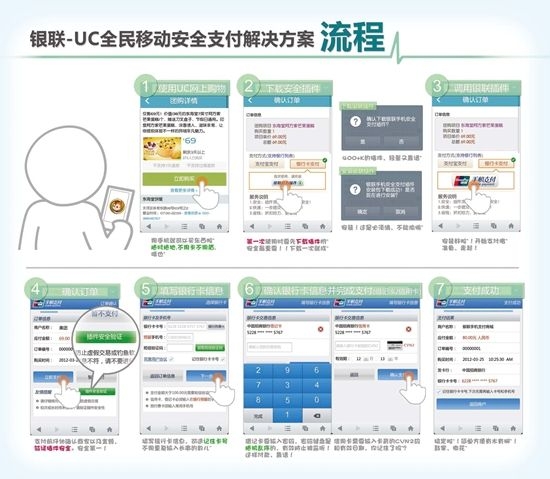

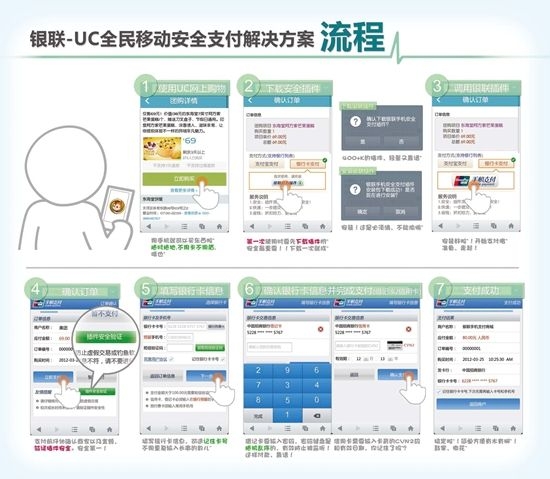

4月24日下午消息,中国银联与UC浏览器今日宣布推出基于UC浏览器的银联移动安全支付解决方案。使用UC浏览器8.3版本的用户可以在手机浏览器内使用银联信用卡或借记卡进行手机支付。

相较于以往的手机支付方案,银联UC移动支付方案相对方便快捷,用户下载相应的银行插件后,填写相关的银行卡信息,就可以以完成支付。

现在很对国内的智能手机用户支付的时候都选择支付宝,不过现在又有了一个新选择。这次方案覆盖的平台包括 Symbian ,iOS,Android 和 Windows Phone ,Java 平台,实际上就是将银联手机支付控件嵌入 UC 手机浏览器或商户手机客户端,来完成支付。相应配合的外设包括具备安全支付功能的金融智能 SD 卡和基于 NFC 技术的手机终端;当然这些需要手机厂商推动,按照发布的信息来看,其已经有了诺基亚,三星,HTC 等合作伙伴。从另一个角度上来看,其安全把关包括 UC 提供的对假冒网站及钓鱼插件的过滤,银联则提供支付安全插件;剩下的选择权就留给用户了,就看你对这个新支付方式的接受程度了;当然多一个选择终归是有好处的。

在手机支付的安全性上,UC优视公司技术总裁梁捷表示,银联-UC全民移动安全支付解决方案与银联的PC支付解决方案有同等安全等级,甚至更高。UC优视采取了浏览与支付分离的技术架构,浏览网页安全由UC浏览器管理,UC浏览器会对假冒网页和假冒支付插件进行提醒,支付的安全则交给银联安全支付插件。

对于未来的目标,UC优视董事长兼CEO俞永福表示,目标是到2013年有超过1000万用户使用银联-UC移动安全支付解决方案。

据了解,中国银联是全球主要银行卡组织,建设和运营银联跨行交易清算系统,目前,全球银联卡发卡量超过29亿张,银联网络遍布中国城乡,并扩展到全球125个国家和地区。UC浏览器全球累计下载量超过15亿次,用户规模超过3亿。据有关调研数据显示,2012年一季度,UC浏览器占49.5%的市场份额,在国内手机浏览器市场中名列第一。

银联UC移动支付解决方案支付流程

|

|

| |

作者 陈怀临 | 2012-05-03 16:09 | 类型 行业动感 | 19条用户评论 »

作者 free-arm | 2012-05-03 16:07 | 类型 图书推荐, 弯曲推荐, 新兴技术 | 25条用户评论 »

|

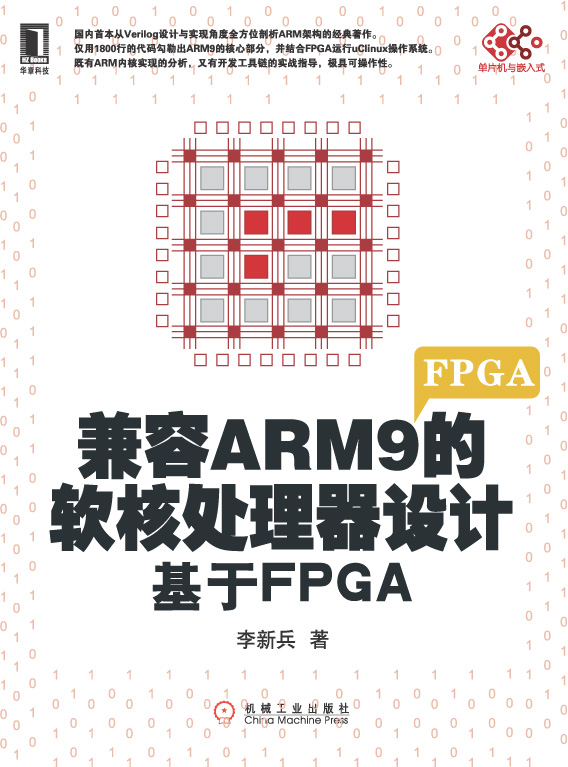

这是一本描述如何使用硬件描述语言Verilog进行FPGA设计的参考书。按照本书的指导,读者可以设计一个32位的RISC架构处理器—兼容市面上流行的ARM9微处理器。读者在完成RTL编程后,可以在购买的FPGA开发板上运行ARM9兼容的嵌入式程序。 这是一本描述如何使用硬件描述语言Verilog进行FPGA设计的参考书。按照本书的指导,读者可以设计一个32位的RISC架构处理器—兼容市面上流行的ARM9微处理器。读者在完成RTL编程后,可以在购买的FPGA开发板上运行ARM9兼容的嵌入式程序。

使用Verilog HDL进行编程到底属于硬件设计还是软件设计?这是一个很难回答的问题。它处于传统的硬件设计和软件设计的交叉点:描述的对象是硬件,但采用的方法和软件设计类似。市面上充斥着各种介绍Verilog HDL设计的书,但都是以介绍Verilog HDL的语法为主,兼而给出一些简单逻辑的Verilog RTL描述。但没有一本书介绍如何使用这种精简的语言进行成熟作品的设计,本书填补了这方面的空白。

一个成功的RTL设计将是价值连城的,譬如ARM公司的系列处理器内核,它们都是采用Verilog等硬件描述语言进行描述设计的,用户如果想使用这些处理器内核,将需要付出昂贵的授权费用。正因为设计出成熟的RTL作品非常难,因此很多书籍对此回避,或者大而化之。好比我们在市面上看到的旅游指南书,都是连篇累牍地介绍该国的地理概貌、风土人情,以及各种介绍数据;但是这样的书籍并不受读者欢迎,而那些由旅游者介绍的各种攻略,由于有旅游者的现身说法,使人读了以后有种身临其境的感觉,受到了读者的热捧。本书尝试做一个Verilog RTL设计攻略的尝试,以流行的RISC处理器为目标,向读者传授编写Verilog程序的第一手的经验和体会。

正因为设计出成熟的RTL程序比较难,很多公司的诸位同仁虽然口头上大力宣扬“创新”的重要性,同他交谈简直是口不离“创新”,言不离“变化”,但如果真的要他稍微改改样儿,则反而会认为非常不稳妥。指原因很简单,所谓创新,所谓变化,初期总是不稳定的,总是没有受到时间检验的,能够直接“盈利”的项目是不会稍稍“改样”来做检验创新的实验品的。于是,我们的创新要成长为众人接受的稳态的变化,需要走很长很长的一段路。幸而,在FPGA设计上,可以接受这种创新、这种变化。因为FPGA是可以不断重复可编程的,如同我们练习毛笔字的那种蘸水写的字帖,练完后,等字迹一干,下次再练不受任何影响。也就是说,读者只需要一块FPGA开发板,加上掌握了一定的Verilog RTL设计技巧,你也就和进行最高端的处理器设计的公司,比如ARM、MIPS等公司站在同一条起跑线上,他们能做的,你也能做。

处理器设计在我们眼里之所以是那么高不可攀,原因就在于这只是为少数公司所掌握的,并不是为大众所能够掌握的技能。对于RISC处理器,我们都知道三级流水线、五级流水线,但都没有一个生动的例子来显示这三级流水线是如何工作的,是如何协调数据、指令的关系。也许有这样的开源的32位的RISC处理器设计,但都非常复杂,读者要弄懂它们,要花费大量的工夫。而且,市面上最主流的处理器是ARM公司推出的一系列RISC处理器,读者对它们的架构与指令集都有所了解。基于此,作者针对ARM9的指令集与架构,介绍Verilog RTL设计,以便读者了解处理器设计的架构,能够在FPGA上真正运行一个32位的RISC处理器。

对于FPGA设计,最重要的是能够在开发板中运行起来。开源的32位RISC处理器开发出来了,它最大的功效是能够帮助FPGA设计者在实际中应用,而不是成为一个展览品,供大家解剖学习。对于本书开发的兼容ARM9微处理器,全部的Verilog RTL描述只有不到1800行代码,存放在一个文件当中。FPGA设计者只需明白设计的I/O接口,即可例化在设计者的设计当中,可以最大化地方便设计者。同时,由于ARM9的开发工具众多,相关的嵌入式软件设计人员也占据了主流,因此,在嵌入式软件资源方面,兼容ARM9处理器的应用会受到这些因素支持。读者在本书中得到了兼容ARM9处理器的Verilog RTL设计后,可以在网络资源以及从事嵌入式软件开发的朋友中得到支持,以在FPGA设计应用中,真正实现完全自我掌握的SoC设计。

长久以来,我国的处理器设计水平落后于欧美国家。虽然龙芯在基于MIPS的架构上有所突破,但在更加流行的ARM架构上鲜有建树。众所周知,以Intel为代表的CISC处理器设计所采用的技术高深,设计过程复杂,在后面的追赶者望尘莫及。有些人在看到Intel的高科技设计水平后,自叹弗如,于是对其他人在处理器上的追赶嗤之以鼻。这就好比看见西方人吃西餐礼节繁琐、堂而皇之,于是自惭形秽,觉得还不如不吃饭了。殊不知吃饭不仅有西餐的吃法,而且还有快餐式的KFC、麦当劳式的吃法。ARM和MIPS就好比饮食界的肯德基与麦当劳。他们为业界提供了RISC架构的处理器,这些处理器都是采用硬件可综合语言编写而成的,易于其他芯片设计公司集成。这种设计方式生产简便、灵活快速,深受其他芯片设计公司欢迎。这就好比快餐式的做法,业界一致摒弃了Intel这种西餐式的吃法。读者如果有志于在处理器设计方面进行突破,那么掌握Verilog RTL的设计技巧,对处理器进行钻研,一定会有所拓展。

本书以Verilog RTL设计为核心,从第1章建立Verilog RTL设计模型开始,到最后一章能够对Linux操作系统进行仿真。读者通过本书可以切实掌握到基于ARM9的数字电路设计流程,并能够利用成熟的MCU软件设计工具生成BIN文件,通过BIN文件和一个只有1800行代码的兼容ARM9处理器内核,读者能够快速完成FPGA设计。

第1章的主要目的是建立Verilog RTL设计的模型。我们知道,进行Verilog RTL设计,必须先具有基本的硬件思维,使得在编写软件式的Verilog代码时,能够时时刻刻警惕自己写的每一行代码都会对应着实体逻辑。这一章会对数字电路的基本模型进行梳理,在这个基础上,我们才能进行复杂逻辑的组织与设计。

第2章基于第1章建立的基本模型,采用硬件模型,使用Verilog语言进行基本的电路设计。首先,分析了Verilog这种硬件描述语言的语言特点。它是一种非常类似C的编程语言。针对RTL设计,它只有寥寥的几种格式。正如我们手机上的笔画输入法,正是这三四种格式,经过组合变换,可以写出各种各样复杂的逻辑。在掌握了Verilog RTL的语言特点后,这一章将带领读者进行串口通信的设计。串口通信涉及串行收发数据,是硬件设计中离不开的调试接口。通过该章建立的设计理念,只需寥寥几十行代码就可以设计一个高效的Verilog RTL程序。

第3章介绍了Modelsim仿真。Verilog RTL设计第一步的检验是进行仿真。该章建立了仿真的基本流程。读者可以通过编写task函数来定制激励,比如在对UART串口进行仿真时,可以通过一个task函数把并行数据串行发送到RTL设计的输入端口上。

第4章介绍了FPGA及FPGA开发板。FPGA是一种奇妙的芯片,它可以模拟各种数字电路的功能—只要我们按照RTL的规则编写了数字电路,FPGA就能很快成为这种功能的芯片。单独的FPGA就如同人的大脑,但如果离开了手臂、腿脚以及眼耳鼻舌等,那再聪明的大脑也不会有所作为。以FPGA为核心的FPGA开发板就如同人脑和人身体结合在一起一样,在我们编写的程序的指导下,FPGA开发板可以实现各种特定的功能。但如果再进一步,把32位的RISC处理器放置于FPGA内部,那么我们指挥“FPGA”的效率就会进一步提高。该章除了对FPGA和FPGA开发板介绍以外,还通过具体的串口通信例子,零实践指导读者对FPGA开发板进行了解。

第5章着重介绍了ARM9TDMI这种曾经风靡一时,现在仍发挥着巨大作用的处理器架构。ARM9的嵌入式开发人员应该对ARM9的编程模型了如指掌,特别是系统设计工程师,必须熟悉汇编级的应用,才能对系统进行调试。该章将从设计的角度对微处理器的中断和指令集进行解读。我们看到的介绍ARM9的指令集都是从一条条的汇编指令的角度入手的,但是本书通过指令集的各种指令的结构把它们总结成了20类指令。于是,对第6章提出了一个课题:如何在一个.v文件内实现20条指令和7种中断。

第6章是本书的核心,它将结合之前章节讲述的知识点,共同呈现出这只有1800行的ARM9微处理器代码。从RTL的角度看,它是由一条条关于寄存器和组合逻辑的描述组成的;从ARM9的编程模型的角度看,它必须实现ARM9架构的20条指令和7种中断;从处理器流水线的角度来看,它必须在三级执行、五级执行之间进行折中;从FPGA执行的角度来看,它必须适应FPGA的结构,在时序和面积之间折中。可以说,Verilog RTL编程就如同带着镣铐的舞蹈,在受到种种约束的情况下,还要跳出优美的舞蹈。该章将以简为纲,尽量把复杂的东西通过简洁的描述呈现给读者。让读者不仅能够理解它,而且在使用时,也能够很轻易地融入到自己的设计中。

第7章介绍了兼容ARM9处理器内核运行的第一个程序—Hello World。在学习C语言时,学习的第一个程序就是输出Hello World。在做好了一个兼容ARM9的处理器设计后,最美妙的事莫过于在开发板中通过串口同样通过C语言描述输出Hello World。现在看看我们具有的元素:FPGA开发板、串口、处理器内核,只要我们通过ARM公司自家流行的RealView MDK以任意一款流行的ARM9 MCU为原型,就可以编写出BIN文件。这些BIN文件在例化入FPGA内的ROM后,它就从死的状态变成活跃的了。我们将看到,这些代码指挥FPGA通过串口输出任何字符串。这一简单的例子将使大家享受到SoC设计带来的乐趣,在以后的FPGA设计中可以尽量使用处理器来简化繁琐的设计流程。

第8章介绍了兼容ARM9处理器内核性能测试—Dhrystone Benchmark。我们知道了处理器的功效,但还不知道这款兼容ARM9的微处理器内核的性能如何。本章将延续第7章的SoC设计流程,对这款处理器内核进行体检,以便获得关于它的第一手资料。经过该章的测试后,我们发现,这款兼容处理器内核可以达到1.2 DMIPS/MHz。

第9章介绍了uClinux仿真—结合SkyEye,启动不带MMU的操作系统。有了FPGA和处理器内核的结合,本书将具有另外一个主旨,那就是把操作系统引入设计当中。SkyEye作为一款软件模拟处理器的工具,它可以作为我们这款内核的标尺,衡量它运行现代流行操作系统的能力。操作系统虽然复杂,但我们同样可以通过编写一个简单的testbench的方式,结合1800行代码构成的处理器内核,让这款操作系统也能在Modelsim中运行。经过仿真,可以看到,它可以输出同SkyEye同样的log信息。硬件工程师通过该章同样可以了解到MCU的构成。

第10章介绍了Linux操作系统—结合mini2440开发板,启动带MMU的嵌入式操作系统。在该章中,读者可以看到开发ARM9兼容处理器内核的优势:它能够得到的帮助实在是太多了。我们不仅有软件模拟器,而且还有市面上极为流行的ARM9开发板。通过开发板,我们可以看到Linux操作系统启动起来,现在,通过编写一个tb文件,我们同样能够在Modelsim中再现ARM9处理器是如何启动Linux操作系统的。本书不同于其他只是介绍性质的书籍,通过实际的仿真步骤,我们能够清晰地理解Linux操作系统是如何与处理器内核结合在一起的。

最后,本书附录提供了带有注释的兼容ARM9处理器内核的Verilog RTL描述。读者可以在这1800行的代码中体会Verilog RTL编程的巧妙之处,以便融会贯通,应用在自己的设计当中。如果能够在设计中应用这款处理器内核,那将是笔者最大的欣慰。

|

|

| |

作者 高飞 | 2012-05-02 22:05 | 类型 行业动感 | 5条用户评论 »

|

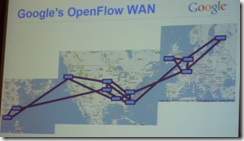

故事的源头要从2005年1月,CNET和Lightreading几乎同时报道Google购买暗纤(Dark Fiber)的新闻开始【1】。这两家机构不约而同的推测,Google可能在建造自己的全球光纤骨干网。当时Google的一则招聘新闻被发掘出来——招聘一位全球基础设施战略谈判家(Strategic Negotiator for Global Infrastructure)。工作职责是这样写的:

"Identification, selection, and negotiation of dark fiber contracts both in metropolitan areas and over long distances as part of development of a global backbone network; contracts and negotiation for managed metropolitan services and long haul wavelength services to fulfill capacity and redundancy requirements in North America, Latin America, Asia, and Europe."中文翻译:作为全球骨干网络建设的一部分,在城域和长距离范围内进行暗纤确定、选择和合同谈判;针对城域业务管理和长距离波分业务管理签订合同与谈判,以满足北美、拉美、亚洲和欧洲的容量和冗余要求。

Dark fiber,暗纤这个词特指已经铺设但未投入使用的光缆,或者是在已经敷设的光缆中,暂时没有使用的光纤。在北美就有数千英里的暗纤,这可以算是上一次互联网泡沫期间基础设施膨胀的产物。暗纤沉睡的另一个原因让其投入运营的费用高昂,没有多少公司愿意在此投资。

多家媒体向Google求证这个职位和其方向,Google拒绝置评。不过这个职位至少反映了当时Google对于自身带宽需求增长的预测。以往购买暗纤的客户一般都是数据需求量巨大的机构如银行,其目的基本上是降低长期运营成本。互联网泡沫破灭后,购买暗纤的客户大多是大型财团、大学、研究机构和医疗机构,很多机构背后都有政府的支持。最著名的例子恐怕是National LamdaRail(NLR),NLR到目前为止占研究机构购买暗纤总量的三分之一强。此外美国第一大有线运营商Comcast也投资数亿美元购买暗纤来建网。

暗纤在泡沫之后的确相对便宜。不过对于很多公司来说,租还是买的问题很好回答。由于买暗纤、点亮、建网是一个耗时数年、耗资巨大的工程,对于大部分公司而言其网络需求决定了,从运营商手里租“亮纤”更便宜,也能避免给华尔街的财报上出意外。因此在这些买暗纤的客户中,Google就显得很特别——不是财团,不是研究机构,不是运营商,Google的这个举措让坊间纷纷猜测其自建基础设施的目的。

Google有为数众多的数据中心(目前超过五十个),自有光纤,更有利于在这些数据中心之间传输“东西向”流量,无论是数据同步还是新辟服务,这些都有利于降低成本来提高用户体验。饶是如此,点亮暗纤的巨大投资还是让坊间猜测,除此之外,Google有没有为进入电信业做准备?

参考文献:

【1】http://news.cnet.com/Google-wants-dark-fiber/2100-1034_3-5537392.html

|

|

| |