弯曲推荐:SandyBridge Spans Generations

作者 mike.yang | 2011-01-26 18:29 | 类型 芯片技术, 行业动感 | 2条用户评论 »

Nehalem的遗憾——英特尔Sandy Bridge处理器分析测试之一

作者 Lucifer | 2011-01-18 11:22 | 类型 专题分析, 弯曲推荐, 芯片技术 | 21条用户评论 »

系列目录 英特尔Sandy Bridge处理器分析测试

原文发布于《计算机世界》2011年第3期

Nehalem 的遗憾 ——英特尔Sandy Bridge 处理器分析测试之一 计算机世界实验室 盘骏 英特尔的“Tick-Tock” 战略已经为人熟知,根据这个策略,英特尔每年都会交替在处理器的制程和微架构上进行更新。上一年,英特尔将处理器工艺从45nm 提升到了32nm,今年,英特尔将处理器架构从Nehalem 升级到最新一代的Sandy Bridge,这个早期被叫做Gesher(希伯来文:桥梁)的处理器微架构担任着特别的桥梁角色。 Bridge 和Gesher 都含有桥梁的意思。而Sandy Bridge 微架构将这个含义发挥到了极致,它是一个集NetBurst 微架构与Nehalem 微架构大成的产品,也是一个首先将CPU和GPU 进行真正融合的产品,更是一个首先将浮点运算密度从128 位引向256 位的X86 处理器产品,它确实像是一个桥梁,引导着芯片设计上和计算模式上的转变。 Sandy Bridge 微架构为什么会是现在这个样子呢? Sandy Bridge 在上一代Nehalem 微架构的基础上进行改进,如果不了解Nehalem 微架构,就无法真正理解Sandy Bridge的进化。 Nehalem 无疑是一个很成功的架构,QPI、IMC 带来的直联架构,再加上超线程的回归,其性能比起上一代提升了一到两倍以上,在企业级市场、主流乃至高端桌面市场以及移动市场的压倒性的占有率充分地说明了Nehalem 的强大。当然,Nehalem 微架构也不是完美的,以笔者的眼光看来,至少有几点Nehalem 微架构是有待改进的: 指令拾取和预解码 Nehalem 微架构在Pentium M微架构的基础上进行改进,整个流水线上几乎所有的组件都得到了增强,变化最少的就是在指令拾取和预解码阶段了。这个阶段的作用是将要执行的指令从L1 I-Cache 中提取到CPU 核心里面来,并随后对其进行预解码。预解码的主要作用就是在一块代码块中辨认每条x86 指令的长度。 和Penryn 一样,Nehalem 以及其改良版Westmere 都仍然采用了16Bytes 的指令拾取宽度,而竞争对手早已经采用了32Bytes 的拾取宽度。由于x86 指令的长度可以从1到15Bytes,因此在很糟糕的情况下,某个时钟周期拾取到的代码块里只包含一个x86 指令,和后端动辄6个、4 个uop(微指令)的能力不相符合。Nehalem 微架构的指令拾取/预解码单元无法跟上后端处理的速度,因此在运行计算密集型的代码中,它很容易成为瓶颈。 寄存器读停顿 这个情形发生在uop 经过RAT(Register Alias Table,寄存器别名表)进行寄存器重命名并发往ROB(ReOrder Buffer,重排序缓冲)之后,在这个被称为ROB-read 的流水线阶段中,uop 们需要读取相关的操作数,也就是读取对应的寄存器,如果这些内容在ROB 当中不存在的话。Nehalem 微架构的RAT 每时钟周期可以输出4 个uop,每个uop可以具有最多两个输入寄存器。这样它最多需要同时读取8 个寄存器。不幸的是,Nehalem 微架构用于保存寄存器的RRF(Retirement Register File,回退寄存器文件)仅具有3 个读取端口,无法充分满足寄存器读取的需求,这很容易导致ROB-read 以及前方流水线的停顿。 访存能力 Nehalem 微架构具有6 个执行端口,其中的3 个运算端口具有充足的计算能力,基本不会是瓶颈。然而,访存能力却不一定足够。Nehalem 微架构只有一个Load 载入端口和一个Store 保存端口。由于Load 操作是如此常见,可以达到uop 总数的1/3,因此相对于3 个运算端口,这个Load 端口是个潜在的瓶颈,特别是对于内存密集型计算来说。 最后, 早期的Nehalem 架构上还存在大页面TLB 数量较少的问题,TLB:Translation Lookaside Buffer,旁路转换缓冲,或称为页表缓冲,里面存放的是虚拟地址到物理地址的转换表。Nehalem 具有较多的标准4KB 页面TLB 项,但是更大容量页面的TLB 很少,因此,相对来说不适合大规模内存下的应用(如大型数据库和大型虚拟化环境,后来的Westmere 通过增加了对1GB 页面的支持缓解了这个问题)。 除了Nehalem 微架构的一些问题之外,英特尔或者说CPU 本身还面临着挑战,来自GPU 的挑战。目前,主要的GPU 厂商包括NVIDIA和AMD ATI 都提供了超越CPU 的强劲浮点处理能力,很多超级计算机通过采用了附加GPU 的方式获得了很强的计算指标。CPU 能力的增强导致了如硬件解压卡、独立声卡被融合进CPU,而GPU 强大的处理能力则被认为是CPU 的有力挑战者。如果运算能力足够强大,CPU 被GPU 取代也不无可能,英特尔怎么应对这个局面? Sandy Bridge 进行了什么样的改进、能不能解决这些问题呢?请看下回分解。 | |

弯曲评论荣誉推荐–Intel Nehalem-EP深度剖析

作者 陈怀临 | 2011-01-13 18:19 | 类型 专题分析, 芯片技术 | 14条用户评论 »

|

【陈怀临注:谢谢Lucifier;谢谢盘骏。谢谢168。得到这份整理好的材料后,我立刻打印了一份。准备好好学习。也希望对x86体系结构有兴趣的研发人员有所帮助。。。Again,你的知识属于你;更属于这个社会。希望大家都奉献。】 | |

“The Pentium Chronicles”摘录

作者 KISS | 2011-01-02 18:05 | 类型 芯片技术 | 7条用户评论 »

|

作者注:下文是”The Pentium Chronicles”一书的阅读摘要,个人最喜欢的一本书之一。双芯记里留言看不到原书的朋友可以翻一翻,结合研读弯曲首席的系统设计方法论,相信不日就可向老板要求大力加薪。作者前文已经介绍过,Intel的前首席IA32架构师,97年的fellow。这本书详细描述了从1990年作者单独来到俄勒冈组建设计团队,到发布P6处理器的历程,以及后续领导Pentium4开发;除此之外,也穿插了许多有趣故事和技术看法:例如访问MS时NT团队和95团队拍桌子对骂数个小时,向Carmack致敬,对Pentium4设计组织的不满-市场团队压过技术团队拥有最终技术决策权,对IPF开发的不满,FPU臭虫的背后故事等等等。书中多处引用萧伯纳,歌德等文字,看得出鲍勃也是一个文艺青年,不知道上不上豆瓣。 The Pentium Chronicles FOREWORD Many of us dreamed of changing the world with great ideas in processor design. I personally experienced the conceptual phase and the refinement phase as part of a four-person team. There were many questions that we tried to address with our limited ability to formulate a potential design and acquire simulation data. In respect, we left many issues not addressed; our project generated many more questions than we answered. It was a heraic pioneer-style exploration of designing a speculative out-of-order-execution processor. Bob gives the ultimate principles of great project management: acquire the best minds, organize them so that each of then operates within their comfort zone, protect them from the forces of mediocrity, help them to take calculated risks, and motivate them to tie up the loose ends. -WEN-MEI HWU | |

DSP . 华睿一号 . 核高基

作者 陈怀临 | 2011-01-01 19:32 | 类型 芯片技术, 行业动感 | 9条用户评论 »

|

中国人民在DSP领域(也)站起来了。DSP领域的核高基项目华睿一号取得重大突破。。。在我大宋12月27日新闻联播中高调播出。 “华睿1号”由中国电子科技集团公司第十四研究所、北京国睿中数科技股份有限公司以及清华大学联合研发。其中,在处理器系统设计方面,“华睿1号”采用了 DSP和CPU多核架构设计技术。实测表明,“华睿1号”的处理能力和能耗具有明显优势,代表了我国目前专用DSP芯片的最高水平,芯片的整体技术指标达到或优于国际同类产品水平。同时,“华睿1号”在运行多任务实时操作系统十分稳定”

| |

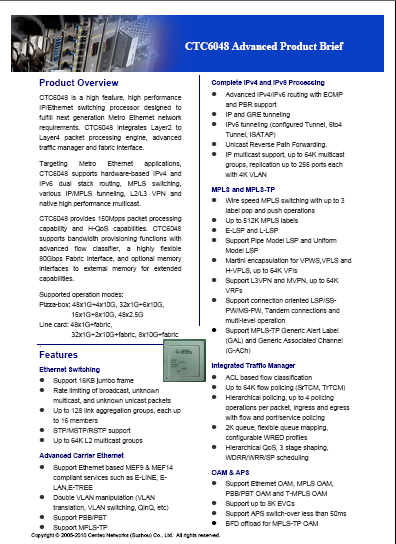

盛科CTC6048参数和MPLS-TP解密

作者 陈怀临 | 2010-12-29 20:11 | 类型 芯片技术, 行业动感, 通讯产品 | 43条用户评论 »

弯曲评论荣誉出品:王齐 。《ARM与x86》

作者 陈怀临 | 2010-12-17 19:29 | 类型 专题分析, 弯曲推荐, 芯片技术 | 14条用户评论 »

|

| |

ARM与x86之5–结束语和参考文献

作者 陈怀临 | 2010-12-16 19:42 | 类型 弯曲推荐, 芯片技术 | 10条用户评论 »

系列目录 ARM与x86

【陈怀临注:请参阅Qi Wang大虾的原文在http://blog.sina.com.cn/sailingxr。等Qi正式上来后,我会把这几篇文章的作者信息都改成他的ID。】 多年以前,我有编写一系列关于处理器体系结构的书籍,包括PowerPC, x86和ARM。两年的坚持,我完成了《Linux PowerPC详解—核心篇》,本应还要写一本《Linux PowerPC详解—应用篇》。我几乎完成了“应用篇”大约三分之一的篇幅,最终放弃。 我的懒惰不是《Linux PowerPC详解—应用篇》没有正式出版的原因。“应用篇”本由网络,USB和PCIe总线三部分组成。网络部分是我较为熟悉的部分,却与处理器体系结构并没有直接的联系,USB总线距离处理器内核也略远一些,只有PCIe总线部分保留下来,形成了《PCI Express体系结构详解》的初步文字。 一次偶然的经历,我有机会使用FPGA设计基于PCIe总线的网络设备。对PCIe总线有了真实的理解后,我将这本书的名字改为“PCI Express体系结构导读”并正式出版。想起详解的书名无地自容,区区几百页的书籍与详解如何能有联系,怕是“导读”也未必有资格。 《PCI Express体系结构导读》的出版,没有带给我喜悦,更多的是如释重负。瞬间的平静后,我准备重新书写“x86体系结构导读”这本书籍。我起初准备书写“x86体系结构导读”,后写《PCI Express体系结构导读》。我甚至写好了“x86体系结构导读”的前言部分,就是我在“开源”杂志率先发表的《PC的足迹》这篇文章。 “x86体系结构导读”不会面世。我不是选择放弃书写,只是明白x86体系结构大巧大拙,包含着太多的不得已和不透明,我并没有将x86体系结构独立成书的能力。写书是准备了一桶水,给读者倒一杯。我对x86体系结构的理解只限于一杯水。 MIPS是我即熟悉也陌生的体系结构。第一次接触MIPS处理器是通过阅读John和David的”A Quantitative Approach”。阅读这本书的起因是为了完成毕业论文,当时国内并没有引入这本书籍的第二版。借助研究巨型机的便利条件,我们很早就有了这本书的复印件。1千多页的复印件分成四份,也是沉甸甸的。在不断翻译腾挪的过程中,我不自觉地喜欢上了体系结构这门学问,坚持至今。我没有书写MIPS处理器的相关书籍的准备,这些书籍只应属于John和David。 我从”A Quantitative Approach”的第二版开始读起,直到第四版,我逐字反复研读了这本书。除了红楼梦之外,没有任何一本书花费我如此气力。感慨中国在近十年内没有任何人能够写出如此深度的书籍。我们这代人即便站在这些巨人的肩膀上,也无法越过他们的头顶。只有水涨船高,群星捧月。 我们努力,却无法改变所处的平面,无法掩饰着星光黯淡。恨天短,恨中国不够强大。我搁下了科技文字的书写,而去书写我们的近邻,历时一个多月,完成了《又逢己丑》。写这些文字,没有任何想法,只是面对无法改变的现实胸中有股不平之气。《又逢己丑》完稿后,《PCI Express体系结构导读》很快出版。我有了许多空余时间,本想继续着一些微不足道的文字,却已没有思绪。 每一代人都有自己的使命。70年代的人历经变革,未向其父辈饱受磨难,却更多地活在理想中。这一代的绝大多数人没有受到最好的教育,没有过多的继承,最优秀的一群人漂流在海外。世界进入到21世纪,因为这一代人的懈怠,我们没有缩小与其他国家的差距。等到再次励精图治,已悄然老去。 八十年代的人,距离我们太近,看到的更多的是缺点。七十年代面对八十年代的叛逆只有长叹,求人不如求己,却忘记自己也是由叛逆到前卫,由前卫至流行,由流行而怀旧。在某一代也许可以出现某个人可以闪耀古今,也无法改变一代更比一代强这亘古不破的道理。事物的发展如此,人类的进步亦如此。对八十年代不公平的是高企的房价,这是他们失落的重要原因。不要苛求暂时并不属于自己的东西,半套房的付出可以使你们周游列国,钢筋混凝土没有想象中重要。 寄寓九十年代。无所求的一代人在有所求的领域必有所得。 4年前,我开始书写一些文字,没有太多目的,或者是在追求着无所求,追求着随遇而安。金钱与声名无法靠写书来实现,只是希望下一代人用最小的代价获得我们千辛万苦积累的这些微不足道,以播下希望的种子。这些苦难也会因此随风而逝。 书写“ARM与x86”是为了自己的心愿。不会写ARM相关的书籍,也不会再苛求纸质的图书,而依然苛求着心愿,不再放弃。以此结束为序。 参考文献 | |

Intel CPU互联方案初探

作者 陈怀临 | 2010-12-12 12:02 | 类型 芯片技术, 行业动感 | 20条用户评论 »

浅谈Intel QPI的MESIF协议和Home,Source Snoop

作者 陈怀临 | 2010-12-05 17:20 | 类型 芯片技术, 行业动感 | 59条用户评论 »

|

Intel的Nehalem一出,CPU江湖顿时失色。其中北桥FSB被灭,CSI/QPI兴起是一个重要因素。也正式宣告了Parallel Bus在处理器领域的王牌地位退出,和Serial Bus或者Point2Point互联的统治地位的诞生。。。:走的快(Parallel Bus)不如走的远(Serial Bus)。 QPI的互联,其中Cache的一致性是一个关键。 其协议是什么?MESIF!与经典的MESI相比,多了一个F word。当然,不是bad words。这里的F是Forwarding的意思。 在上面的两个图中,左边的是MESIF;右边的是经典的MESI。MESIF的例子中,我们可以看见,F状态的存在其实就是为了与S状态区别开来。系统中只有一个F,类比与:在一个家庭中,婆婆与老婆。如果是双重领导,事情全mess up。必须是一个领导F。找数据的时候,F给你,而非S(系统中有许多S)。读者一定要注意,F状态的引入是为了性能,而非状态机的完备性。没有F,S就可以搞定一切[如上右图]。系统中,对任何一个数据的Cacheline,有而且只有一个F。每次一个新人上台,需要数据,F就移交。F变成S。最新的数据变成F。这也是最佳利用Cache算法中的所谓Temporal Locality和Spatial Locality的考量:年轻人一定是会持续工作,时间长的。。。;年老的数据一定不是常用的;持续力不够的。。。另外,读者从上面两图中可以看出,MESI会造成QPI的链路上产生没必要的Snooping Response: 系统里多个婆婆(拥有相同数据备份的node)在非常殷勤的告诉一个申请者:阿拉有数据,and here you go。。。 在Nehalem互联中,QPI可以有Source Snoop或者Home Snoop。通常而言,小规模socket互联用Source Snoop;大规模互联用Home Snoop。 Home Snoop和Source Snoop的本质区别与Snooping时候MESFI状态机的F状态的目的是类似的:在能解决问题的同时,尽量减少互联上的Transaction。例如,Home Snoop的意思就是:老大说了算,负责协调;别人都别吭声。Soure Snoop的意思就是:各个小山头都可以掺和,立功表态。说到这里,就理解了,如果是一个大规模的Nehalem机群互联,用Home Snoop好;如果是1-8个Nehalem互联,估计Source Snoop好一些。道理很简单:如果是一个startup,问一个事,吆喝一声,知道的都回答你,挺好的;如果是一个10万人的公司,发个群发email给10万个人,问一个事情,估计骂你的人比回答你答案的人都多;你最好是问主管(Home)。。。 在上图中,哪个是Home Snoop?哪个是Source Snoop?显然,右图上Home Snoop;左图是Source Snoop。Source Snoop一定是而且只是2 Hop就能搞定数据,while Home Snoop需要在大本营到一下手,需要3 Hop。 MESIF,Intel申请了专利。其专利为: 该专利是2002年12月9日申请的。2005年7月26日批的。 M-blah-blah-I有许多变种。许多读者估计要么会迷糊,要么静不下心来。如果是前者,抓住一个要素:Write Invalidate。 我曾经在若干年前用大白话解释过Write Invalidate协议。学术的东西其实本质很简单。要理解须先要忘记学术,返璞归真。。。 下图是一个MESI的简单状态机。在理解Cache一致性协议状态机的时候,最容易犯迷糊的是把本CPU的动作与Snooping的动作混淆。现在简单忽悠一下这里面的M状态。从M上面围绕的动作,我们可以知道:蓝色的是自已玩自己的动作(发生在本CPU内部的);红色的是监听到友商(别的CPU,或者其他逻辑,反正就是人在江湖,不得不在一起混的那些node,station等等)的动作。M的意思是:我现在是独家拥有,而且我很牛,还独家拥有修改过的数据。我现在自己独乐乐(Local Read;Local Write);显然,没人能拿你怎么样。你多牛呀,你接着当M!……但是,突然在总线(FSB)或者互联(QPI)上监听到了不想看到的事情。。。:(1)有人发生了读行为(Remote Read)。你该如何办?还想一党独大嘛?没天理。你要把最新的数据给人民。。。而且要把数据UPDATE到DRAM里面去。数据是天下人的数据;而非某个CPU的数据!你的状态要变成S(hared)的了。。。。。。(2)有人发生了写行为(Remote Write)。要夺权!!!如何处理!?交权!皇帝轮流转!请把数据交出来,给别人写一写,玩一玩;然后人家变成了M;你自己变成了I(nvalid)了。。。你需要变成S嘛?至少目前没必要,除非你想读。。。。。。 细心的读者估计会反复琢磨这个状态机。请注意I(nvalid)状态的输入!!!严格的一致:全部来自红色的Remote Write–这就是我们说M-blah-blah-blah-I等各种变种协议都来自学术界里的所谓:Write Invalidate Protocol。用大白话就是:写失效。只要我看到别人有写一个数据备份,我就认栽!承认自己是弱势群体。。。。。。变成非法躲猫猫。 下图所示是MESFI,MOESI,MESI状态机的一些比较。Note that AMD的ccHT用的是MOESI。。。 另外,从SerDes的角度来观察QPI。可以这样去理解:QPI是一个Parallel Clock的SerDes。 这就可以理解QPI的Signal(Pin)了。QPI是单向的。信号是21个。20lane(bit)+clock。每个信号是Differential Signal(差分信号)的。因此是20×2 +1×2=42个pin(管脚)。如果一个QPI 端口(Port)【一发,一送,pair】,是84个pin。。。 Intel以前的并行总线Front-side Bus的pin有多少,600+多个!QPI是84个!比一比,吓一跳。 Parallel Clock SerDes是典型的把以前的并行总线信号汇聚成Serial Bus的做法。《控制信号+数据信号+地址信号+时钟)—》时钟+Serialized Signals。 | |

(9个打分, 平均:4.56 / 5)

(9个打分, 平均:4.56 / 5)